“软件设计师精讲 CPU的组成(运算器与控制器)”的版本间的差异

跳到导航

跳到搜索

Jihongchang(讨论 | 贡献) (→CPU结构) |

Jihongchang(讨论 | 贡献) (→CPU结构) |

||

| 第14行: | 第14行: | ||

数据缓冲寄存器:CPU和存储做交互时读写内存时做中转的部件,先中转、再运输。 | 数据缓冲寄存器:CPU和存储做交互时读写内存时做中转的部件,先中转、再运输。 | ||

[[文件:CPU结构3.png|无|缩略图|600x600像素]] | [[文件:CPU结构3.png|无|缩略图|600x600像素]] | ||

| + | |||

| + | === 运算器 === | ||

| + | '''算数逻辑单元ALU:数据的算数运算和逻辑运算''' | ||

| + | |||

| + | 累加寄存器AC:通用寄存器,为ALU提供一个工作区,用在暂存数据 | ||

| + | |||

| + | 数据缓冲寄存器DR:写内存时,暂存指令或数据 | ||

| + | |||

| + | 状态条件寄存器PSW:存状态标志与控制标志 | ||

| + | |||

| + | (争议:也有将其归为控制器的) | ||

| + | |||

| + | === 控制器 === | ||

| + | '''程序计数器PC:存储下一条要执行指令的地址''' | ||

| + | |||

| + | 指令寄存器IR:存储即将执行的指令 | ||

| + | |||

| + | 指令译码器ID:对指令中的操作码字段进行分析解释 | ||

| + | |||

| + | 时序部件:提供时序控制信号 | ||

2024年4月24日 (三) 13:28的版本

https://www.bilibili.com/video/BV13U4y1E7oA/?p=12

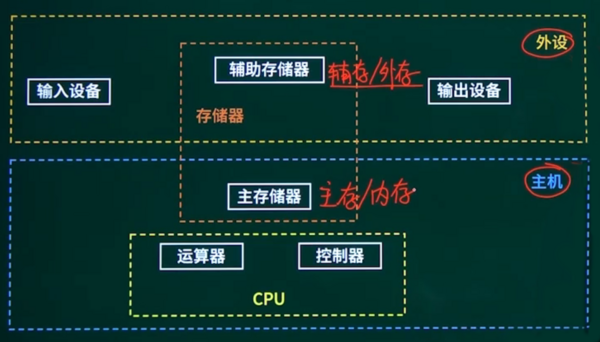

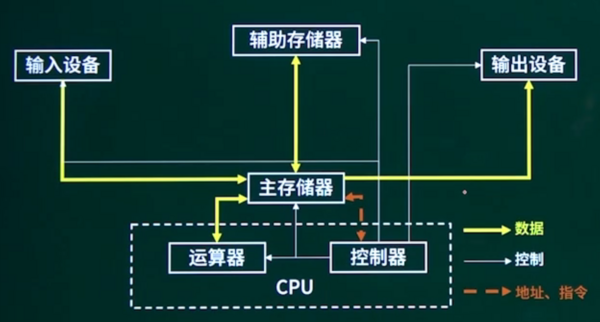

计算机结构

CPU结构

状态条件寄存器的归属存在争议:也可能划分到控制器中。

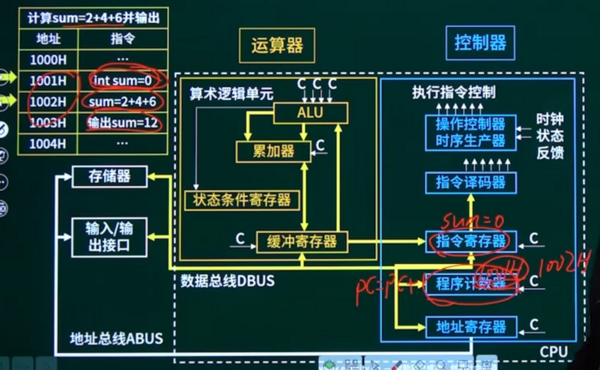

算术逻辑单元:做算术逻辑运算。

累加寄存器(AC):放算术逻辑单元进行数据加工的数据材料,也是为ALU提供工作区的部件。

数据缓冲寄存器:CPU和存储做交互时读写内存时做中转的部件,先中转、再运输。

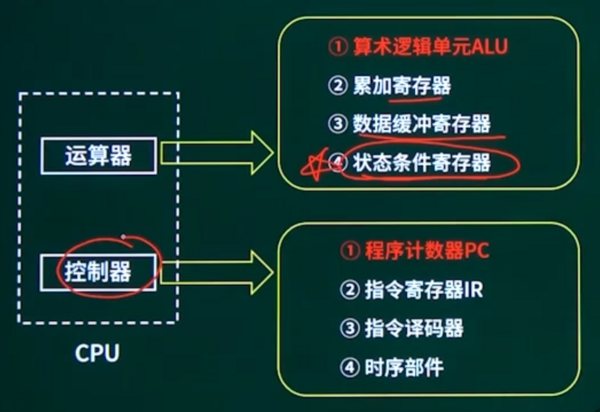

运算器

算数逻辑单元ALU:数据的算数运算和逻辑运算

累加寄存器AC:通用寄存器,为ALU提供一个工作区,用在暂存数据

数据缓冲寄存器DR:写内存时,暂存指令或数据

状态条件寄存器PSW:存状态标志与控制标志

(争议:也有将其归为控制器的)

控制器

程序计数器PC:存储下一条要执行指令的地址

指令寄存器IR:存储即将执行的指令

指令译码器ID:对指令中的操作码字段进行分析解释

时序部件:提供时序控制信号