“软件设计师精讲 CPU的组成(运算器与控制器)”的版本间的差异

Jihongchang(讨论 | 贡献) (→CPU结构) |

Jihongchang(讨论 | 贡献) (→例题讲解) |

||

| (未显示同一用户的9个中间版本) | |||

| 第7行: | 第7行: | ||

=== CPU结构 === | === CPU结构 === | ||

[[文件:软件设计师精讲 CPU结构.png|无|缩略图|600x600像素]]状态条件寄存器的归属存在争议:也可能划分到控制器中。 | [[文件:软件设计师精讲 CPU结构.png|无|缩略图|600x600像素]]状态条件寄存器的归属存在争议:也可能划分到控制器中。 | ||

| + | |||

| + | 算术逻辑单元:做算术逻辑运算。 | ||

| + | |||

| + | 累加寄存器(AC):放算术逻辑单元进行数据加工的数据材料,也是为ALU提供工作区的部件。 | ||

| + | |||

| + | 数据缓冲寄存器:CPU和存储做交互时读写内存时做中转的部件,先中转、再运输。 | ||

| + | [[文件:CPU结构3.png|无|缩略图|600x600像素]] | ||

| + | |||

| + | 这个程序的目的是计算2+4+6,然后赋值给sum,通过sum返回。 | ||

| + | |||

| + | 里面的过程包含声明、定义,sum的初值等于0,计算sum的值,输出sum的值。 | ||

| + | |||

| + | 在这个过程当中,程序在计算机当中肯定是存储起来的,存储的地址依次有个相应的地址编号。 | ||

| + | |||

| + | 在运算的过程当中,先看控制器。控制器会控制计算机按照这些指令依次完成相应的功能。 | ||

| + | |||

| + | 首先,要想读取到程序,我们会将程序的起始位置读入到指令的'''<big><u>程序计数器</u>(PC)</big>'''当中,会将1001H记录进去。 | ||

| + | |||

| + | 1001H是一个地址,根据地址,可以找到指令“int sum=0”,把这个指令放到'''<big><u>指令寄存器</u>(IR)</big>'''当中去。 | ||

| + | |||

| + | 放进去之后,这个1001H就没用了,内容已经找到了。 | ||

| + | |||

| + | 所以接下来会给PC一个新的赋值:PC=PC+1,变成了1002H,这个过程就是顺序读取的过程。 | ||

| + | |||

| + | 如果涉及到条件判断跳转的话,这里可以是偏移量代替加1的过程。 | ||

| + | |||

| + | 当读到'''<big><u>指令寄存器</u>(IR)</big>'''当中,它的内容并不是“sum=0”,而是以一定的0、1二进制字符串表示,这个字符串如何体现在计算机当中的软、硬件呢? | ||

| + | |||

| + | 会通过'''<big><u>指令译码器</u>(ID)</big>'''翻译,告诉软硬件做哪些动作,这就是<u>程序计数器</u>(PC)、<u>指令寄存器</u>(IR)以及<u>指令译码器</u>(ID)的功能。 | ||

| + | |||

| + | 在这中间,还有一些控制信号、时序信号会通过时序部件传输。这里面有一个<u>'''<big>地址寄存器</big>'''</u>没有提到,它是使用的时候,用来保存内存地址的。 | ||

| + | |||

| + | 这些就是'''<big>程序控制器</big>'''。 | ||

| + | |||

| + | 除了程序控制器以外,CPU还有一部分是运算器部分。 | ||

| + | |||

| + | 运算器就是做算术逻辑运算的,就是做计算的,在进行2+4+6的运算过程的时候,是如何顺序计算的? | ||

| + | |||

| + | 首先,第一步,计算的是2+4=6,第二部计算6+6=12,在这中间的6怎么处理呢? | ||

| + | |||

| + | 在这个过程当中进行加法运算的过程是在'''<big><u>算术逻辑单元</u>(ALU)</big>'''当中进行的<big>,</big>中间的“6”是个中间数据,暂存在<u>累加寄存器</u>,也就是'''<big><u>累加器</u>(AC)</big>'''当中''','''它可以给ALU提供数据加工的材料,也可以给ALU提供工作区。 | ||

| + | |||

| + | 得出的结果12有个进位,进位标志会记录在状态条件寄存器党中,记录它的状态标志。 | ||

| + | |||

| + | 记录完之后,如果这个状态标志当中,有一些会用来做控制标志、控制条件,这个时候,它也可以归于控制器的范畴,最终会输出sum=12。 | ||

| + | |||

| + | 输出会通过输入/输出设备来进行输出,甚至可能会写到存储器当中去,与外部这些内容做交互的话,会通过缓冲寄存器中转数据,这些就是运算器当中的具体过程。 | ||

| + | |||

| + | === 运算器 === | ||

| + | '''算数逻辑单元ALU:数据的算数运算和逻辑运算''' | ||

| + | |||

| + | 累加寄存器AC:通用寄存器,为ALU提供一个工作区,用在暂存数据 | ||

| + | |||

| + | 数据缓冲寄存器DR:写内存时,暂存指令或数据 | ||

| + | |||

| + | 状态条件寄存器PSW:存状态标志与控制标志(争议:也有将其归为控制器的) | ||

| + | |||

| + | === 控制器 === | ||

| + | '''程序计数器PC:存储下一条要执行指令的地址''' | ||

| + | |||

| + | 指令寄存器IR:存储即将执行的指令 | ||

| + | |||

| + | 指令译码器ID:对指令中的操作码字段进行分析解释 | ||

| + | |||

| + | 时序部件:提供时序控制信号 | ||

| + | |||

| + | === 例题讲解 === | ||

| + | 计算机中提供指令地址的程序计数器PC在()中。 | ||

| + | |||

| + | A、控制器 √ | ||

| + | |||

| + | B、运算器 | ||

| + | |||

| + | C、存储器 | ||

| + | |||

| + | D、I/O设备 | ||

| + | |||

| + | |||

| + | CPU执行算术运算或者逻辑运算时,常将源操作数和结果暂存在()中。 | ||

| + | |||

| + | A、程序计数器(PC) | ||

| + | |||

| + | B、累加器(AC) √ | ||

| + | |||

| + | C、指令寄存器(IR) | ||

| + | |||

| + | D、地址寄存器(AR) | ||

2024年5月7日 (二) 13:36的最新版本

https://www.bilibili.com/video/BV13U4y1E7oA/?p=12

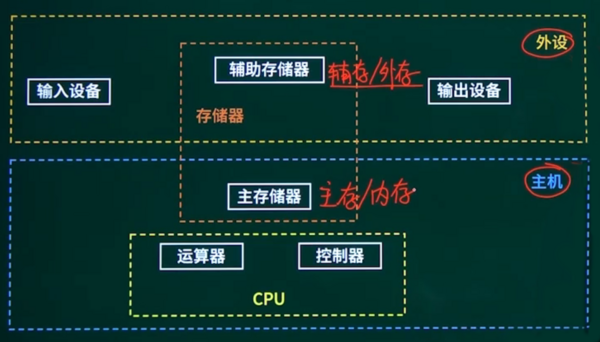

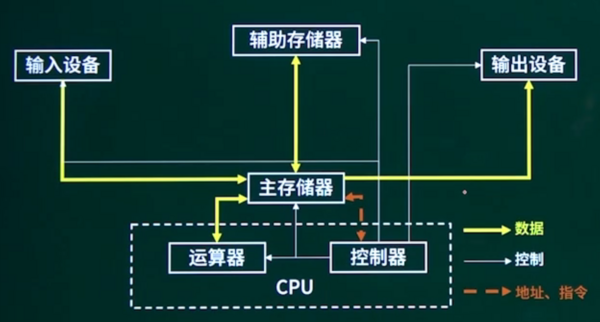

计算机结构

CPU结构

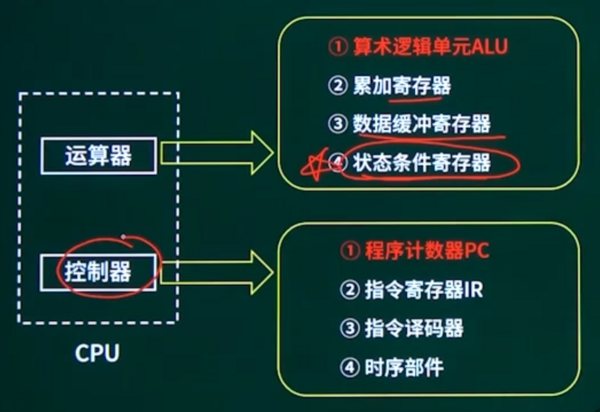

状态条件寄存器的归属存在争议:也可能划分到控制器中。

算术逻辑单元:做算术逻辑运算。

累加寄存器(AC):放算术逻辑单元进行数据加工的数据材料,也是为ALU提供工作区的部件。

数据缓冲寄存器:CPU和存储做交互时读写内存时做中转的部件,先中转、再运输。

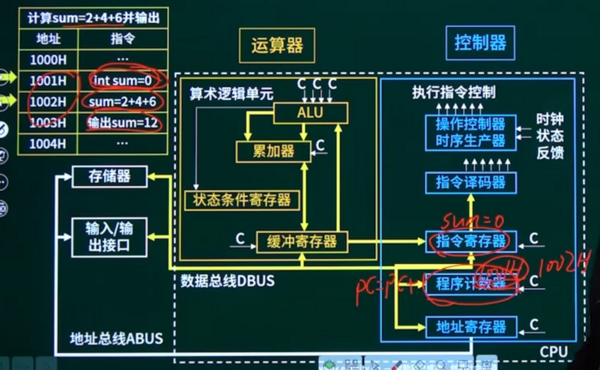

这个程序的目的是计算2+4+6,然后赋值给sum,通过sum返回。

里面的过程包含声明、定义,sum的初值等于0,计算sum的值,输出sum的值。

在这个过程当中,程序在计算机当中肯定是存储起来的,存储的地址依次有个相应的地址编号。

在运算的过程当中,先看控制器。控制器会控制计算机按照这些指令依次完成相应的功能。

首先,要想读取到程序,我们会将程序的起始位置读入到指令的程序计数器(PC)当中,会将1001H记录进去。

1001H是一个地址,根据地址,可以找到指令“int sum=0”,把这个指令放到指令寄存器(IR)当中去。

放进去之后,这个1001H就没用了,内容已经找到了。

所以接下来会给PC一个新的赋值:PC=PC+1,变成了1002H,这个过程就是顺序读取的过程。

如果涉及到条件判断跳转的话,这里可以是偏移量代替加1的过程。

当读到指令寄存器(IR)当中,它的内容并不是“sum=0”,而是以一定的0、1二进制字符串表示,这个字符串如何体现在计算机当中的软、硬件呢?

会通过指令译码器(ID)翻译,告诉软硬件做哪些动作,这就是程序计数器(PC)、指令寄存器(IR)以及指令译码器(ID)的功能。

在这中间,还有一些控制信号、时序信号会通过时序部件传输。这里面有一个地址寄存器没有提到,它是使用的时候,用来保存内存地址的。

这些就是程序控制器。

除了程序控制器以外,CPU还有一部分是运算器部分。

运算器就是做算术逻辑运算的,就是做计算的,在进行2+4+6的运算过程的时候,是如何顺序计算的?

首先,第一步,计算的是2+4=6,第二部计算6+6=12,在这中间的6怎么处理呢?

在这个过程当中进行加法运算的过程是在算术逻辑单元(ALU)当中进行的,中间的“6”是个中间数据,暂存在累加寄存器,也就是累加器(AC)当中,它可以给ALU提供数据加工的材料,也可以给ALU提供工作区。

得出的结果12有个进位,进位标志会记录在状态条件寄存器党中,记录它的状态标志。

记录完之后,如果这个状态标志当中,有一些会用来做控制标志、控制条件,这个时候,它也可以归于控制器的范畴,最终会输出sum=12。

输出会通过输入/输出设备来进行输出,甚至可能会写到存储器当中去,与外部这些内容做交互的话,会通过缓冲寄存器中转数据,这些就是运算器当中的具体过程。

运算器

算数逻辑单元ALU:数据的算数运算和逻辑运算

累加寄存器AC:通用寄存器,为ALU提供一个工作区,用在暂存数据

数据缓冲寄存器DR:写内存时,暂存指令或数据

状态条件寄存器PSW:存状态标志与控制标志(争议:也有将其归为控制器的)

控制器

程序计数器PC:存储下一条要执行指令的地址

指令寄存器IR:存储即将执行的指令

指令译码器ID:对指令中的操作码字段进行分析解释

时序部件:提供时序控制信号

例题讲解

计算机中提供指令地址的程序计数器PC在()中。

A、控制器 √

B、运算器

C、存储器

D、I/O设备

CPU执行算术运算或者逻辑运算时,常将源操作数和结果暂存在()中。

A、程序计数器(PC)

B、累加器(AC) √

C、指令寄存器(IR)

D、地址寄存器(AR)